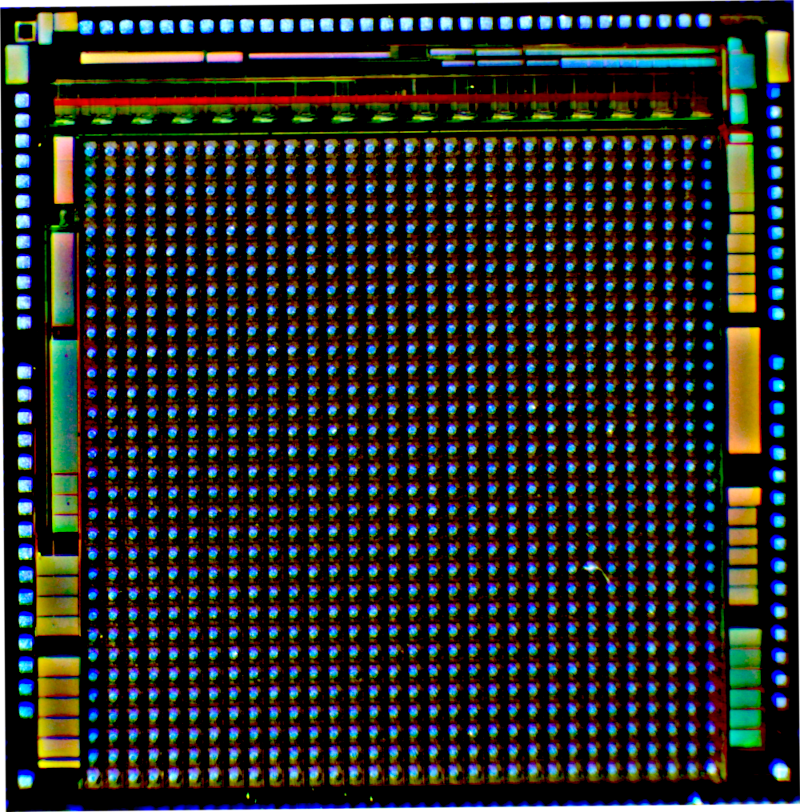

High‑Channel Neural ASIC

A next‑generation mixed‑signal ASIC engineered for high‑density neural recording, low‑noise amplification, and scalable integration into research and clinical systems.

Technology Overview

Our custom neural ASIC integrates high‑channel‑count amplification, digitization, and data multiplexing into a compact, low‑power architecture suitable for implantable, wearable, and benchtop systems.

- Low‑noise front‑end amplifiers

- High‑density channel integration

- Configurable gain and bandwidth

- Low‑power digitization pipeline

- Available as bare die or packaged for evaluation

Early Access Program

We’re partnering with a select group of research labs, device teams, and early‑stage companies evaluating our high‑channel neural ASIC for next‑generation interfaces. Early access provides priority support, evaluation hardware, and opportunities for deeper technical collaboration.

- Prototype ASICs fabricated, tested, and available in limited quantities

- Evaluation hardware offered to qualified teams (small handling + shipping fee)

- Limited early‑access units released each quarter

- Designed for research labs, device companies, and robotics teams building advanced neural systems

We recognize that integrating new ASICs can involve packaging, firmware, and system‑level work. If you’re excited about the technology but see adoption challenges ahead, we’d still encourage you to reach out — we’re exploring funding pathways and partnerships that could help support teams working on these integration efforts, and we want to understand where the biggest needs are as we shape the program to reduce the lift for early adopters.

Request Samples

For evaluation units, research collaborations, or integration discussions, submit a request below.

Why We Built This ASIC — and What Partners Should Know

ASIC Availability

-

Why make the ASICs available if LithopsBio is building a platform?

Because they’re enabling infrastructure. High‑channel‑count neural interfaces are a pre‑competitive layer: when the foundational tools are widely accessible, the entire field moves faster. Broad availability expands adoption, accelerates downstream innovation, and reinforces our position at the infrastructure layer. This follows the same pattern used by other infrastructure companies that expand adoption by making the enabling layer widely accessible.

-

Does offering the ASICs reduce LithopsBio’s defensibility?

Not at all. Our long‑term differentiation lies in the system, software, and cloud‑lab layers—not in restricting access to the silicon. Making the chips available accelerates adoption and reinforces our position as the default infrastructure provider.

ASIC Technical Positioning

-

What kinds of systems can these ASICs support?

They’re optimized for high‑channel‑count, low‑power neural interfaces and integrate cleanly into next‑generation recording, stimulation, and closed‑loop systems across research, robotics, and device development.

-

Why are these ASICs suitable beyond their original rodent‑focused design?

The constraints of freely behaving rodent electrophysiology forced extreme efficiency, robustness, and signal quality — properties that translate directly to broader applications in scalable, high‑density neural systems.

ASIC Development History

-

What applications were these ASICs originally designed for?

They were engineered to support high‑fidelity electrophysiology in freely behaving rodents, where size, power, and data‑quality constraints are extreme. That heritage is why they’re compact, low‑power, and robust across a wide range of next‑generation neural recording systems.

-

How does NIH funding influence your distribution strategy?

NIH support seeded the foundational technology, and broad access is part of ensuring that publicly funded tools accelerate the entire field. That openness strengthens the ecosystem while LithopsBio focuses on building the differentiated system, software, and cloud‑lab layers that sit above the silicon.